Tiny210 U-BOOT(七)----SDRAM工作时序与原理

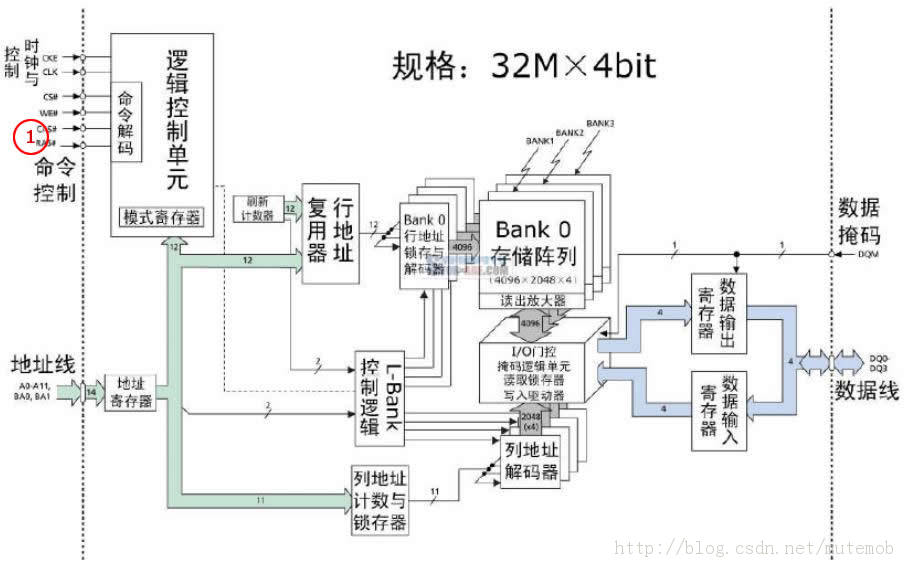

DDR出身自SDRAM,严格的说应该叫DDR SDRAM,DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思,所以,有很大一部分,两者是一样的,理解SDRAM,然后再来理解DDR在SDRAM上的改进,效果应该更好一些,这里要感谢Chinaunix.net的大神--Tekkaman Ninja,我的内存的学习资料都是Tekkaman Ninja的博客中介绍的。以下是我对大神推荐文档的一些个人整理,OK,先上一张SDRAM的结构图。

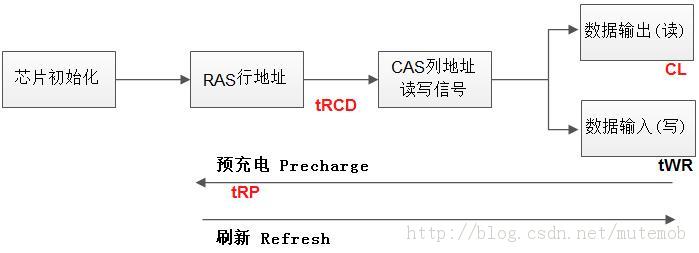

下面上一张我画的简易的SDRAM工作流程图

图中用红色标明的就是我们需要找的几个主要时间,现在开始看图说话。

1.芯片初始化

SDRAM 芯片内部有一个逻辑控制单元,并且有一个模式寄存器为其提供控制参数。因此,每次开机时 SDRAM 都要先对这个控制逻辑核心进行初始化。

2.行有效

初始化完成后,要想对一个 L-Bank 中的阵列进行寻址,首先就要确定行(Row),使之处于活动状态(Active),然后再确定列。简单点理解就先传行地址过来。

3.列读写

行地址确定之后,就要对列地址进行寻址了。读写的信号和列地址是同时发过来的,读写的操作取决于WE#引脚,当他使能则为写,否则为读。

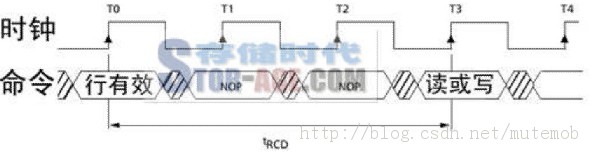

在发送列读写命令时必须要与行有效命令有一个间隔,这个间隔被定义为 tRCD,即RAS to CAS Delay(RAS 至 CAS 延迟),大家也可以理解为行选通周期,简单点理解就是说,在发完行地址后,再发列地址和读写信号时,需要延迟一下,这应该是根据芯片存储阵列电子元件响应时间(从一种状态到另一种状态变化的过程)所制定的延迟。

广义的 tRCD 以时钟周期(tCK,Clock Time)数为单位,比如 tRCD=2,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,对于PC100 SDRAM,tRCD=2,代表1000/100 * 2 = 20ns 的延迟,下图是tRCD=3的时序图。

4.数据输出(读)

在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据 I/O 通道(DQ)输出到内存总线上了。

但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为 CL(CAS Latency,CAS 潜伏期)。由于CL只在读取时出现,所以 CL 又被称为读取潜伏期(RL,Read Latency),下图是CL=2的示意图。

5.数据输入(写)

数据写入的操作也是在 tRCD 之后进行,但此时没有了 CL(记住,CL 只出现在读取操作中),行寻址与列寻址的时序图和上文一样,只是在列寻址时,WE#为有效状态。

为了保证数据的可靠写入,都会留出足够的写入/校正时间(tWR,Write Recovery Time),这个操作也被称作写回(Write Back)。tWR 至少占用一个时钟周期或再多一点(时钟频率越高,tWR 占用周期越多)

以上就是SDRAM是主要工作步骤,对比一下最上面的简易工作流程图,时间是不是就很清楚了呢?

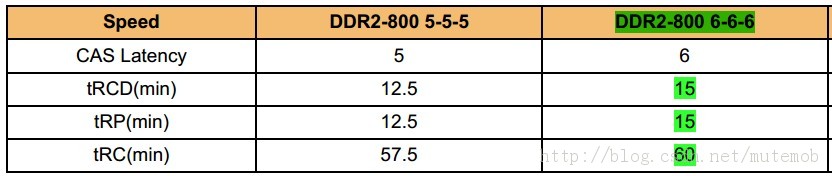

CL=6:CAS Latency,CAS 潜伏期,CAS与读取命令发出到第一笔数据输出的时间 ----读操作

tRCD=6:RAS to CAS Delay(RAS 至 CAS 延迟),行地址发完后,再发列地址的延迟时间 ----行列地址延迟

tRP=6:关闭现有工作行,准备打开新行,经过一段时间才能允许发送 RAS 行有效命令打开新的工作行的时间 ----预充电时间

OK,至此三个时间全部清清楚楚了。