Intel80386知识总结: 多任务支持

====================================================================

本文用于汇总整理Intel80386的多任务支持功能,

参考文献:

《INTEL 80386 programmer's reference manual 1986》

本文是系列文章《Intel80386知识总结》的一部分。

===================================================================

1. 任务信息的管理机构

1.1 TSS

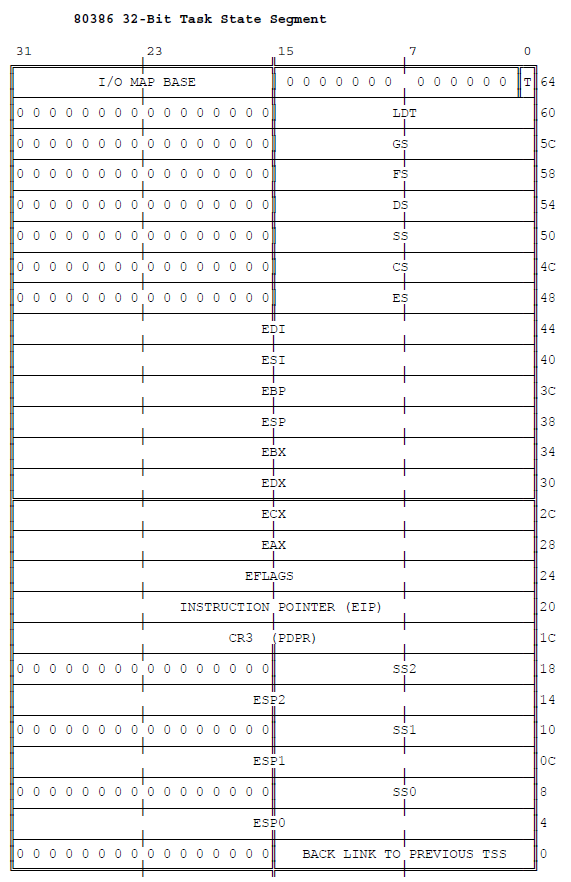

处理器把维护一个任务所需的所有信息都保存在一个特殊的段中:Task State Segment(TSS)。TSS的结构如下图所示:

TSS中的字段可以分为两组,一组是每次任务切换时都会更新的动态字段,另一组是只读的静态字段。动态字段包括:

通用寄存器保存字段:EAX、ECX、EDX、EBX、ESP、EBP、ESI、EDI段寄存器保存字段:ES、CS、SS、DS、FS、GS标志位寄存器保存字段:EFLAGS指令指针保存字段:EIP前一个任务的TSS选择符

静态字段包括:

任务LDT的选择符寄存器PDBR的保存字段CPL为0~2时的堆栈段选择符,共3个T bit:Debug trap bit,等于1时,在每次任务切换时处理器都会产生一个调试异常I/O Map base:I/O用

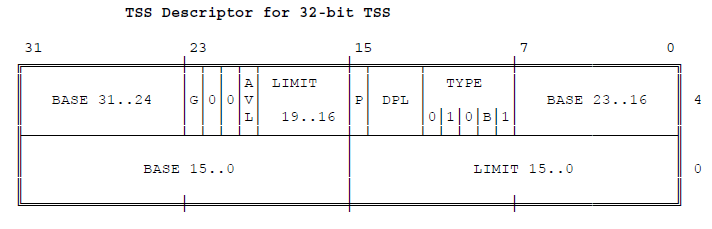

1.2. TSS描述符

即指向TSS的段描述符,其结构如下所示:

TSS描述符TYPE字段中的B bit是TSS的忙标志位,当TYPE字段=9时,表示该任务为非繁忙任务,当TYPE字段=11时,表示该任务为繁忙任务。i386的任务是不可重入的,处理器可以通过检查任务的B bit发现任务是否繁忙。TSS描述符的LIMIT字段必须大于等于103,大于103是允许的,可以系统软件被用来存储一些相关信息。

TSS描述符只能被保存在GDT中,通过TI=1的选择符访问TSS选择符会造成异常。不能直接通过把TSS描述符载入数据段寄存器来修改其中的内容,只能通过载入另一个指向TSS的数据段描述符来修改TSS。

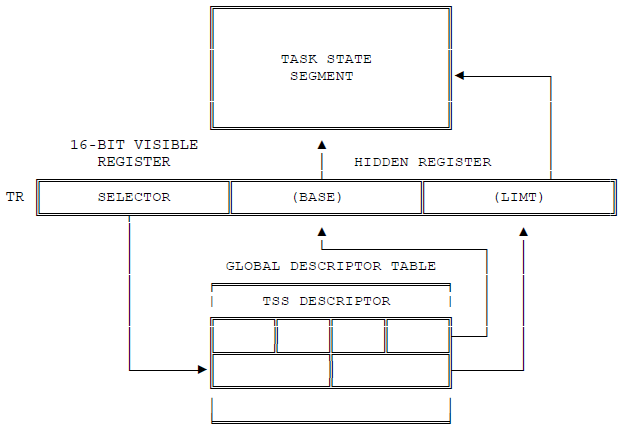

1.3. TR寄存器

TR寄存器给出了当前任务的TSS,通过TR寄存器访问TSS的路径如下图所示:

1.4. 任务门

i386提供任务门机制作为间接的受保护的访问TSS的方式,其结构如下所示:

其中,SELECTOR字段指向TSS描述符,SELECTOR字段中的RPL是不被使用的,同时,当使用任务门时,TSS描述符中的DPL失效,优先级保护规则为:选中任务门所用的选择符RPL和CPL都必须小于等于任务门的DPL。

一个TSS只有唯一的TSS描述符与其对应,却可以有多个任务门同时指向对应的TSS。TSS描述符和任务门形成了多任务管理的两层架构:

2. 任务的切换

2.1 切换流程

检查当前任务是否有权切换到目标任务:TSS描述符或者是调用门的DPL必须小于等于CPL和调用门选择符的RPL检查目标TSS描述符的PRESENT字段是否为1,LIMIT字段是否合法,否则产生异常。异常将在切换前的任务上下文中。保存当前任务的执行现场:保存寄存器EAX、ECX、EDX、EBX、ESP、EBP、ESI、EDI、ES、CS、SS、DS、FS、GS、EFLAGS到TSS。把当前指令(造成任务切换的指令)的下一条指令地址保存到TSS。在TR寄存器中载入目标任务的TSS描述符,并设置其Busy bit。从新任务的TSS中恢复现场,并继续执行

在上述过程中要完成的保护检查一览: